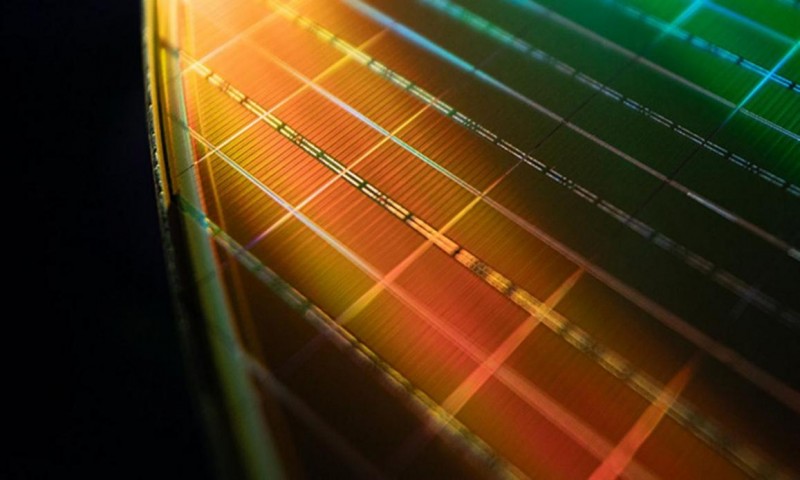

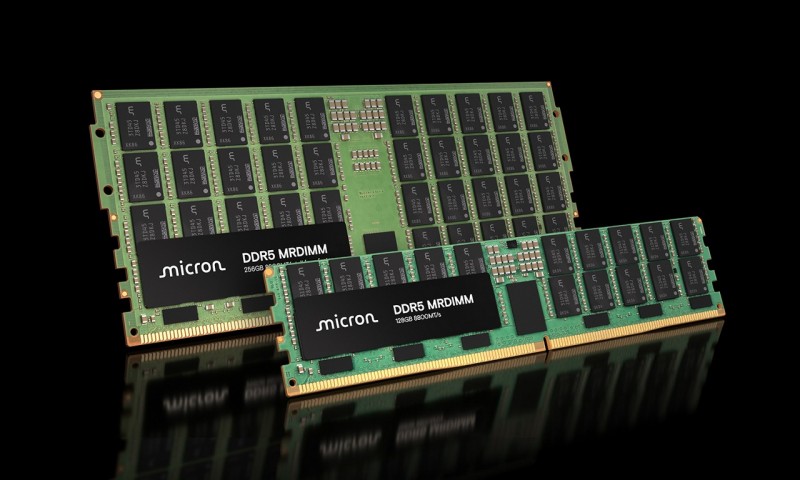

在半导体存储领域持续创新的美光科技,近期通过多项技术突破再次巩固其行业领先地位。最新量产的1γ工艺节点DDR5内存成为技术标杆,9200MT/s的传输速率配合20%的功耗降低,重新定义了高性能内存的能效标准。这项成就得益于极紫外光刻(EUV)技术的精妙应用——仅在关键制造层使用EUV,配合深紫外光刻(DUV)多重曝光工艺,在保证30%密度提升的同时有效控制成本。更值得关注的是其高K金属栅极晶体管设计,使信号传输效率显著提升,为AI服务器等需要高带宽的应用场景提供了硬件基础。

在三维堆叠技术方面,美光232层3D NAND芯片展现了存储密度的飞跃。通过CFET晶体管技术的引入,相较前代产品实现了40%的密度提升。这种立体架构的创新不仅扩大了单颗芯片的容量,更通过优化电荷存储结构,将漏电流控制在极低水平,大幅延长了存储设备的使用寿命。西安制造基地的测试数据显示,采用新技术的SSD在连续写入测试中保持稳定的性能曲线,这在超大容量数据存储场景中具有重要价值。

封装技术的突破同样引人注目。台湾工厂量产的HBM3E高带宽存储器采用12层硅通孔堆叠设计,1024bit超宽总线使其单封装带宽达到1.2TB/s,相当于每秒传输40部4K电影的数据量。这种突破性性能源自两项核心技术:铜硅混合键合工艺将TSV通孔间距缩小至35μm级别,而非对称散热结构通过阶梯式导热柱设计使热阻系数降低40%。在实际应用中,该技术已证明能将AI模型训练的数据供给延迟从传统内存的18微秒压缩到6.8微秒,显著提升计算效率。

面对多元化的市场需求,美光在西安生产基地的战略布局显得尤为关键。该基地扩展的移动DRAM与SSD测试能力,可满足每年8000万台智能终端的存储需求。特别在车规级存储领域,三重防护设计(硼硅玻璃封装层、石墨烯电磁屏蔽膜、自修复ECC算法)使产品在-30℃极端环境下仍能保持3毫秒以内的稳定访问延迟。工业级模块的耐久性同样出色,振动测试显示经过200万次机械冲击后误码率仍低于10^-16量级,相当于连续运行23年不出现单个比特错误。

市场策略方面,美光展现出灵活的技术过渡方案。Multi-Mode BIOS技术通过可编程阻抗匹配电路、动态时序调节器和协议转换引擎三大组件,使同一主板可自动适配DDR4-3200至DDR5-6400的内存规格。某省级政务云平台的实践表明,该方案使服务器过渡期采购成本降低34.6%,同时保持99.999%的服务可用性。在移动端,Dynamic Burst技术能智能识别图像信号处理器的数据流模式,1.2毫秒内完成存储bank配置切换,使高端手机的RAW连拍缓存深度提升3倍以上。

从技术路线图观察,美光正在构建完整的内存生态系统。1γ节点作为基础平台,将逐步整合到DDR5、LPDDR5X等多种产品线中。新加坡70亿美元投资的HBM封装工厂预计2026年投产后,将进一步增强在人工智能内存市场的供给能力。这种全链条的技术布局,既确保了当前产品的性能优势,也为应对未来AI算力需求的指数级增长做好了准备。

郑重声明:此文内容为本网站转载企业宣传资讯,目的在于传播更多信息,与本站立场无关。仅供读者参考,并请自行核实相关内容。